本章概述了页的情况,后续再补充4篇文章来说明4种页。

分页(或线性地址转换)是转换线性地址以便它们可用于访问内存或 I/O 设备的过程。分页将每个线性地址转换为物理地址,并为每个转换确定允许对线性地址的访问(地址的访问权限)以及用于此类访问的缓存类型(地址的内存类型)。

分页模型和控制bit

分页行为是通过以下4个寄存器中的控制位置来决定的:

1.控制寄存器CR0中的WP(bit 16)和PG(bit 31)标志位。

2.控制寄存器CR4中的PSE(bit 4), PAE(bit 5), PGE(bit 7), LA57(bit 12), PCIDE(bit 17), SMEP(bit 20), SMAP(bit 21), PKE( bit 22,), CET(bit 23,), PKS(bit 24)标志位

3.IA32_EFER MSR 中的LME (bit 8 )和 NXE(bit 11)

4.EFLAGS寄存器中的AC(bit 18)标志位。

软件通过使用MOV CR0指令设置CR0.PG来启用分页。 在这样做之前,软件应确保控制寄存器CR3包含处理器将用于线性地址转换的第一个分页结构的物理地址,并确保该结构已根据需要初始化。 有关在不同的分页模式(mode)下使用CR3的信息,参见表4-3,表4-7和表4-12。

表4-3

使用32bit分页时CR3的使用情况

| bit位 | 内容 |

|---|---|

| 2:0 | 忽略 |

| 3(PWT) | 页级直写; 在线性地址转换期间间接确定用于访问页目录的内存类型 |

| 4(PCD) | 页面级缓存禁用; 在线性地址转换过程中间接确定用于访问页目录的内存类型 |

| 11:5 | 忽略 |

| 31:12 | 用于线性地址转换的 4 KB 对齐页目录的物理地址 |

| 63:32 | 忽略(这些位仅存在于支持 Intel-64 架构的处理器上) |

表4-7

使用PEA分页的CR3

| bit位 内容 | |

|---|---|

| 4:0 | 忽略 |

| 31:5 | 用于线性地址转换的 32 字节对齐页目录指针表的物理地址 |

| 63:32 | 忽略(这些位仅存在于支持 Intel-64 架构的处理器上) |

表4-12

4级页和5级页的CR3并且CR4.PCIDE = 0

| bit位置 | 内容 |

|---|---|

| 2:0 | 忽略 |

| 3(PWT) | 页级直写; 在线性地址转换期间间接确定用于访问 PML4 表的内存类型 |

| 4(PCD) | 页面级缓存禁用; 在线性地址转换期间间接确定用于访问 PML4 表的内存类型 |

| 11:5 | 忽略 |

| M-1:12 | 用于线性地址转换的 4 KB 对齐 PML4 表或 PML5 表的物理地址 |

| 63:M | 保留(必须为 0) |

注意这里的M是MAXPHYADDR的缩写,最多为52;

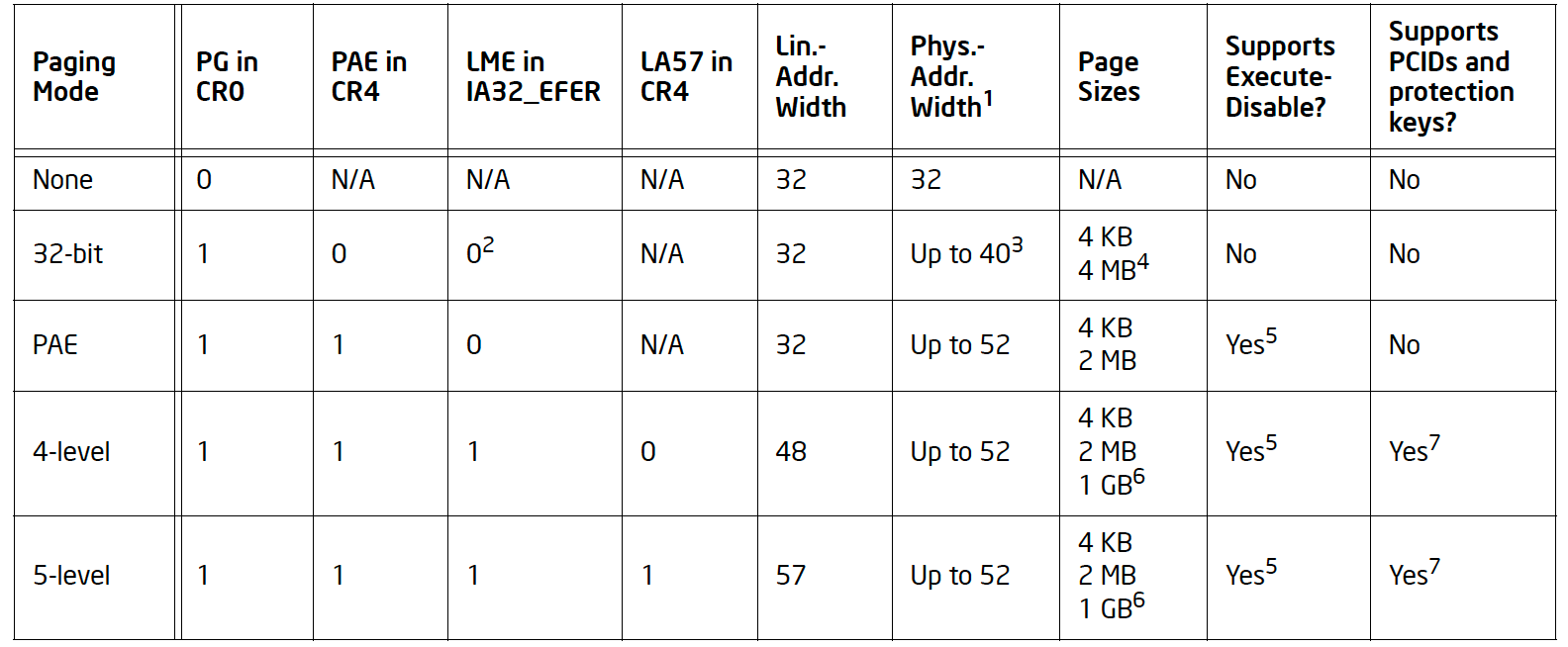

四种分页模型

如果CR0.PG = 0,则不使用分页。 逻辑处理器将所有线性地址视为物理地址.CR4.PAE,CR4.LA57和IA32_EFER.LME被处理器忽略,CR0.WP,CR4.PSE,CR4.PGE,CR4.SMEP, CR4.SMAP和IA32_EFER.NXE。(在影响线性地址访问权限的范围内,CR4.CET也被忽略。)

如果CR0.PG = 1,则启用分页功能。只有在启用保护(CR0.PE = 1)的情况下,才可以启用分页功能。 如果启用了分页,则使用四种分页模式之一。 CR4.PAE,CR4.LA57和IA32_EFER.LME的值确定使用哪种分页模式:

1.如果CR4.PAE = 0,则使用32位分页。

2.如果CR4.PAE = 1且IA32_EFER.LME = 0,则使用PAE分页。

3.如果CR4.PAE = 1,IA32_EFER.LME = 1,并且CR4.LA57 = 0,则使用4级分页

4.如果CR4.PAE = 1,IA32_EFER.LME = 1,并且CR4.LA57 = 1,则使用5级分页

四种分页模式在以下细节方面有所不同:

1.线性地址宽度。可以转换的线性地址的大小。

2.物理地址宽度。分页产生的物理地址的大小。

3.页面大小。线性地址转换的粒度。同一页上的线性地址将转换为同一页上的相应物理地址。

4.支持禁用执行权限。在某些分页模式下,可以防止软件从其他可读的页面中获取指令。

5.支持PCID。通过4级分页和5级分页,软件可以启用一种功能,逻辑处理器可利用该功能为多个线性地址空间缓存信息。当软件在不同的线性地址空间之间切换时,处理器可以保留缓存的信息。

6.支持保护键。在4级分页和5级分页中,每个线性地址都与一个保护密钥相关联。软件可以使用保护密钥权限寄存器为每个保护密钥禁用对与该保护密钥相关联的线性地址的某些访问权限。

由于32位分页和PAE分页仅在传统保护模式下使用,并且由于传统保护模式不能产生大于32位的线性地址,因此32位分页和PAE分页会转换32位线性地址。

4级和5级分页仅在IA-32e模式下使用。 IA-32e模式有两个子模式:

兼容模式。 该子模式仅使用32位线性地址。 在此子模式下,4级分页和5级分页会将此类地址的位63:32视为全0。

64位模式。 虽然此子模式产生64位线性地址,但处理器会强制规范,这意味着该地址的高位相同:用于4级寻呼的位63:47和用于5级寻呼的位63:56。 4级分页(分别为5级分页)不使用此类地址的位63:48(分别为位63:57)。

4种模式的区别如下:

注11.物理地址宽度始终由MAXPHYADDR限制;

注2.如果CR0.PG = 1且CR4.PAE = 0,则处理器确保IA32_EFER.LME必须为0。

注3.32位分页仅在4 MB的页面上并且仅在支持PSE-36机制的情况下才支持大于32位的物理地址宽度。

注4.仅当CR4.PSE = 1时,32位分页才使用4 MB的页

面。

注5.仅当IA32_EFER.NXE = 1时才应用执行禁用访问权限。

注6.支持4级分页或5级分页的处理器不一定支持1 GB的页面。

注7.仅当CR4.PCIDE = 1时才使用PCID。仅在满足某些条件时才使用保护锁;

由于32位分页和PAE分页仅在传统保护模式下使用,并且由于传统保护模式不能产生大于32位的线性地址,因此32位分页和PAE分页会转换32位线性地址。

4级和5级分页仅在IA-32e模式下使用。 IA-32e模式有两个子模式:

兼容模式。 该子模式仅使用32位线性地址。 在此子模式下,4级分页和5级分页会将此类地址的位63:32视为全0。

64位模式。 虽然此子模式产生64位线性地址,但处理器会强制规范,这意味着该地址的高位相同:用于4级寻呼的位63:47和用于5级寻呼的位63:56。 4级分页(分别为5级分页)不使用此类地址的位63:48(分别为位63:57)。

启用分页

如果CR0.PG = 1,则逻辑处理器处于四个分页模式之一,具体取决于CR4.PAE,IA32_EFER.LME和CR4.LA57的值。 图4-1说明了软件如何启用这些模式并在它们之间进行转换。 以下各项确定了某些限制和其他详细信息:

1、启用分页(CR0.PG = 1)时,无法修改IA32_EFER.LME。尝试使用WRMSR这样做会导致一般保护异常(#GP(0))。

2、当CR4.PAE = 0且IA32_EFER.LME = 1时,无法启用分页(通过将CR0.PG设置为1)。尝试将MOV用于CR0会引起一般保护异常(#GP(0))。

3、图4-1中的一个节点标记为“ IA-32e模式”。该节点表示4级分页(如果CR4.LA57 = 0)或5级分页(如果CR4.LA57 = 1)。如以下各项所述,如果不先禁用分页功能,软件将无法修改CR4.LA57(实现4级分页和5级分页之间的转换)。

4、使用4级分页或5级分页时(CR0.PG = 1且IA32_EFER.LME = 1),不能修改CR4.PAE和CR4.LA57。尝试将MOV用于CR4会导致一般保护异常(#GP(0))。

5、无论当前使用哪种分页模式,软件都可以通过MOV将CR0的CR0.PG清空,来禁用分页

6、通过MOV将CR4.PAE的值更改为CR4,软件可以在32位分页和PAE分页之间转换。

7软件不能直接在4级分页(或5级分页)和任何其他分页模式之间进行转换。它必须首先禁用分页(通过将MOV的CR0.PG清除为CR0),然后设置CR4.PAE,IA32_EFER.LME ,然后将CR4.LA57设置为所需的值(将MOV设置为CR4和WRMSR),然后重新启用分页(通过将CR0.PG设置为MOV设置为CR0)。如前所述,在启用4级分页或5级分页的同时尝试修改CR4.PAE,IA32_EFER.LME或CR.LA57会导致一般保护异常(#GP(0))。

8、VMX转换允许使用MOV到CR或WRMSR无法实现的分页模式之间的转换。这是因为VMX转换可以在一项操作中加载CR0,CR4和IA32_EFER。请参阅第4.11.1节。

下图说明了模式切换的情况。

分页层次结构概述

每个分页结构的大小为4096字节,并包含许多单独的条目。使用32位分页时,每个条目为32bit(4字节);因此,每个结构中有1024个条目。在其他分页模式下,每个条目为64bit(8字节);因此,每个结构中有512个条目。 (PAE分页包括一个例外,该分页结构为32字节大小,包含4个64位条目。)。

处理器使用线性地址的前一部分来标识一系列分页结构条目。这些条目把线性地址转换到的区域的物理地址(称为page frame)。线性地址的后一部分(称为page offset)标识了线性地址转换成的那个区域内的特定地址。

每个分页结构条目都包含一个物理地址,该地址可以是另一个分页结构的地址,也可以是页面帧(page frame)的地址。 在第一种情况下,该条目被称为引用其他分页结构。 在后者中,该条目被称为映射页面(map a page)。

用于任何转换的第一个分页结构位于 CR3 中的物理地址。 使用以下迭代过程转换线性地址。 线性地址的一部分选择分页结构中的条目。 如果该条目引用另一个分页结构,则该过程继续使用该分页结构以及紧接在刚刚使用的下面的线性地址部分。 如果条目映射一个页面,则该过程完成:条目中的物理地址是页帧(page frame)的物理地址,线性地址的剩余低部分是页面偏移量。

以下各项给出了四种分页模式中每一种的示例(假设页帧4 KB):

对于 32 位分页

每个分页结构包含 1024 = 2^10 个条目。31:22bit 标识第一个分页结构条目,21:12bit 标识第二个。 后者标识页帧。 线性地址的11:0bit 是 4 KB 页帧内的页偏移量。如下图所示

对于 PAE 分页

第一个分页结构仅包含 4 = 2^2 个条目。 因此,转换开始时使用来自 32 位线性地址的位 31:30 来标识第一个分页结构条目。 其他分页结构包括 512 = 2^9 个条目。29:21bit标识第二个分页结构条目,20:12bit标识第三个。 最后标识了页帧。如下图所示

对于 4 级分页

每个分页结构包含 512 = 2^9 个条目,并且翻译一次使用来自 48 位线性地址的 9 位。 47:39bit 标识第一个分页结构条目,38:30bit 标识第二个,29:21bit 标识第三个,20:12bit 标识第四个。同样,最后一个标识页帧。

对于5级分页

5 级分页类似于 4 级分页,除了 5 级分页转换 57 位线性地址。位 56:48 标识第一个分页结构条目,而其余位用作 4 级分页。

上面每个例子中的翻译过程都是通过识别一个页帧来完成的; 页帧是原始线性地址转换的一部分。 然而,在某些情况下,分页结构可以被配置为使得翻译过程在识别页帧之前终止。 如果进程遇到标记为“不存在”的分页结构条目(因为其 P 标志位 0 已清除)或其中设置了保留位,则会发生这种情况。 在这种情况下,线性地址没有转换; 对该地址的访问会导致页面错误异常。

在上面的例子中,当线性地址中只剩下 12 位时,分页结构条目用 4 KB 的页帧映射一个页面; 前面确定的条目总是引用其他分页结构。 这可能不适用于其他情况。 以下项目标识条目何时映射页面以及何时引用另一个分页结构:

• 如果线性地址中剩余 12 位以上,则查询当前分页结构条目的第 7 位(PS — 页大小)。 如果该位为 0,则该条目引用另一个分页结构; 如果该位为 1,则该条目映射一个页面。

• 如果线性地址中只剩下 12 位,则当前分页结构条目总是映射一个页面(第 7 位用于其他目的)。

如果分页结构条目在线性地址中剩余 12 位以上时映射页面,则该条目标识大于 4 KB 的页帧。 例如,32 位分页使用线性地址的高 10 位来定位第一个分页结构条目; 剩余 22 位。 如果该条目映射一个页面,则页帧为 2^22 字节 = 4 MBytes。如果 CR4.PSE = 1,32 位分页可以使用 4 MByte 页。其他分页模式可以使用 2 MByte 页(无论 CR4.PSE)。 如果处理器支持,4 级分页和 5 级分页可以使用 1 GB 的页面。

分页结构根据它们在翻译过程中的用途被赋予不同的名称。 下表给出了不同分页结构的名称。 它还为每个结构提供用于定位它的物理地址的来源(CR3 或不同的分页结构条目); 用于从结构中选择条目的线性地址中的位; 以及此类条目是否以及如何映射页面的详细信息。

来源:freebuf.com 2021-07-25 17:06:44 by: lhkhk

请登录后发表评论

注册